## SILICON ON INSULATOR TECHNOLOGY REVIEW

Rahul Kr. Singh, Amit Saxena, Mayur Rastogi Deptt. of E& C Engg., MIT, Moradabad, U.P., India singh4491@gmail.com, amitssaksena@yahoo.co.in, mayurrastogi@yahoo.com

#### ABSTRACT

An effort to reduce the power consumption of the circuit, the supply voltage can be reduced leading to reduction of dynamic and static power consumption. This paper introduces one of the greatest future technologies of this decade and that is SOI technology. Silicon-On-Insulator transistors are fabricated in a small (~100 nm) layer of silicon, located on top of a silicon dioxide layer, called buried oxide. This oxide layer provides full dielectric isolation of the transistor and thus most of the parasitic effects present in bulk silicon transistors are eliminated. The structure of the SOI transistor is depicted and is very similar to that of the bulk transistor. The main difference is the presence of the buried oxide it provides attractive properties to the SOI transistor. Power has become one of the most important paradigms of design convergence for multi gigahertz communication such as optical data links wireless products and microprocessor ASIC/SOC designs. POWER consumption has become a bottleneck in microprocessor design. For more than three decades, scientists have been searching for a way to enhance existing silicon technology to speed up the computer performance. This new success in harnessing SOI technology will result in faster computer chips that also require less power a key requirement for extending the battery life of small, hand-held devices that will be pervasive in the future. SOI is a major breakthrough because it advances chip manufacturing one to two years ahead of conventional bulk silicon. The following provides a step-by-step look at the developments leading up to the development of SOI technology.

### I. INTRODUCTION

In the 1960's the requirement for radiation hard devices in the military and space industry resulted in the development of silicon on-insulator devices. Due to the immature manufacturing processes, the manufacturers have been forced to use expensive materials to be able to create the active silicon on top of the insulating layer. Later processes have showed promising properties for the commercial sub nanometre technologies. [147,146] this is why several of the recent CMOS processes are SOI processes and they are expected to become increasingly more common in the future. However, to design a system-on-chip using SOI, one has to be able to compensate for the unwanted effects on the analog circuits, which are due to the use of SOI Traditionally; the two most important criteria used for measuring the performance of a circuit have been speed and area.

However, due to both increased transistor density and the advent of portable electronics an increasingly important cost measure in VLSI design is power consumption.[134,133] While recently a great deal of effort has been put into low power techniques for computation-intensive applications and SOI technology is one of them. Most of the early SOI devices were fabricated with SOS (Silicon-On-Sapphire) wafers. The unique feature of today's SOI wafers is that they have a buried silicon oxide (Buried Oxide, or Box) layer extending across the entire wafer, just below a surface layer of device-quality single-crystal silicon.

The active elements (e.g., transistors in a CMOS IC) of semiconductor devices are fabricated in the single-crystal silicon surface layer over the BOX. [132,131] The BOX layer provides robust vertical isolation from the substrate. Standard LOCOS (Local Oxidation of Silicon) or STI (Shallow Trench Isolation) processes are employed to provide lateral isolation from adjacent devices. [130,129,78]Most of the early SOI devices were fabricated with SOS (Silicon-On-Sapphire) wafers. The unique feature of today's SOI wafers is that they have a buried silicon oxide (Buried Oxide, or BOX) layer extending across the entire wafer, just below a surface layer of device-quality single-crystal silicon. At the present time, most SOI wafers are fabricated by use of one of two basic approaches. SOI wafers may be fabricated with the SIMOXTM ([124,123] separation by Implanted

Oxygen) process, which employs high dose ion implantation of oxygen and high temperature annealing to form the BOX layer in a bulk wafer.

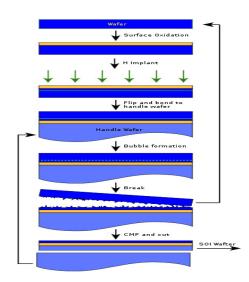

Fig.1. Fabrication of silicon on insulator through oxidation.

Alternately, SOI wafers can be fabricated by bonding a device quality silicon wafer to another silicon wafer (the "handle" wafer) that has an oxide layer on its surface. [145,144] the pair is then split apart, using a process that leaves a thin (relative to the thickness of the starting wafer), device-quality layer of single crystal silicon on top of the oxide layer (which has now become the BOX) on the handle wafer. This [127,51,52] is called the "layer transfer" technique, because it transfers a thin layer of device-quality silicon onto an oxide layer that was thermally grown on a handle wafer. The "layer transfer" approach has lead to the development of at least three production methods for fabrication of SOI wafers; SmartcutTM (UNIBOND) SOI wafers, NanocleaveTM SOI wafers, and ELTRANTM SOI wafers. The SmartcutTM and NanocleaveTM processes both employ high dose ion implantation (using hydrogen or other light species), either alone or in combination with other steps, to form a weakened silicon layer that splits (i.e., "peels off") the donor wafer, allowing the "layer transfer" to occur.

The ELTRANTM method (Epitaxial Layer Transfer) does not use ion implantation. It employs a layer of porous silicon, which is formed by anodic etching and annealing, to form the splitting layer. Recently, there is strong interest in SOI wafers for application to the fabrication of advanced CMOS ICs. [142]This is because SOI wafers provide a way to increase the speed performance of CMOS circuits, as well as reduce the power (and voltage) requirements to achieve high performance. The trade-off between performance and power dissipation is the most fundamentally challenging issue on the horizon for scaling of CMOS ICs.[121,53] This issue threatens the roadmap of continuous scaling of CMOS devices. [54,100]A solution must be found to insure the commercial dominance of CMOS ICs in the future, so it is little wonder that SOI, which offers solutions to this issue, is receiving serious attention at leading-edge companies developing advanced CMOS ICs.[99,118,117] Compared to similar circuits fabricated on bulk silicon wafers, CMOS circuits fabricated on SOI wafers can run at 20-35% higher switching speeds than bulk CMOS, or 2 to 4 times lower power requirements when operating at the same speed as bulk CMOS .

### II. SOI PROSPECTS:

SOI wafers are now viewed as the most important emerging wafer engineering technology for use in leading edge CMOS IC production during the next 3-5 years [115]. One plausible scenario during this period is the rapid adoption of SOI wafers in place of epitaxial silicon wafers now employed as

# International Journal of Engineering Sciences & Emerging Technologies, May 2011.ISSN: 2231 – 6604Volume 1, Issue 1, pp: 1-16 ©IJESET

starting substrates for high-end logic device (e.g., microprocessors) and SOC (System On Chip) applications at the 0.13 and 0.10 micron technology nodes.[3] SOI wafers appear to offer an excellent platform for integrating RF and digital circuits on the same chip. Major semiconductor market research firms have forecasted the possibility that SOI wafers may make up 10% of all silicon wafers used by 2010. Almost all of the "top 20" chipmakers have publicly expressed high interest in the inherent advantages of SOI wafers (e.g., IBM, Intel, AMD, etc.). A bright spotlight was cast on SOI wafer technology production in August 1998 due to an IBM announcement that they would adopt SOI wafer technology using the SIMOX SOI wafer process in high volume manufacturing on leading edge microprocessor architecture. It is in production now, using partially depleted transistor architecture [3,11]. Furthermore, Intel has recently unveiled their vision of the CMOS device they will pursue in the future, to achieve continuous scaling of CMOS with high performance and acceptable power (and voltage) requirements. This is the Intel "Terahertz Transistor", which employs the use of a fully depleted (FD) CMOS transistor on thin SOI wafers [7], among other design changes (such as high-K gate dielectric and raised source-drain regions).

One of the more compelling reasons why support for migration from bulk to SOI CMOS is growing is due to the problems created by the exponential growth of the power dissipated by high performance, high density CMOS ICs in bulk (or epitaxial) silicon as scaling has been pursued [7]. For example, as Intel microprocessors have evolved by scaling through the 286, 386, and 486 generations into and through the Pentium generations, power dissipation has dramatically (exponentially) increased. The 286 generation ran warm (to the touch by your fingers), the 386 ran very hot, and the 486 ran so hot that it needed a small fan to cool it. As evolution proceeded through the Pentium generations, the cooling requirement was more demanding at each generation, using more powerful fans and adding cooling fins to the microprocessor package to improve heat transfer out of the IC. Assuming that the Intel microprocessor stays on its historical trend lines (Moore's Law), in 2005 ICs had about 1 billion transistors and operate at about 10 Gigahertz [114,97]. They will also dissipate so much power that they would require cooling by refrigeration of a liquid coolant in good thermal contact with the IC package. This is unacceptable as a computer systems requirement, and it illustrates that power dissipation is becoming a major barrier to scaling high performance, high density CMOS in the very near future. SOI CMOS offers a way to avoid this barrier without sacrificing high performance or high density.

SOI devices also appear to offer a sustainable, long-term pathway beyond the multiple barriers to scaling planar, bulk CMOS to 50n and below [1,138]. If the present understanding of the barriers and problems to scaling planar, bulk CMOS below 50nm is correct, then it is expected that a dramatic shift to fully depleted SOI CMOS will occur in the[61,70,71] 2006-2008 timeframe. If the many challenges in the fabrication of "ultra-thin" SOI wafers are met (adequate materials quality and acceptable cost), and if device design and lithography challenges are met, the way to 25nm CMOS is open, enabled in part by SOI substrates. SOI wafers will have a very significant impact on both the IC fabrication process and process equipment. For example, [55,120]SOI wafers are fabricated using an ion implantation step employing a high dose of oxygen (Ibis' SIMOXTM SOI wafer process) or hydrogen (SOITEC's SmartCutTM SOI wafer process).

#### III. SOI ADVANTAGES

The SOI [136] wafer structure has several important advantages over CZ bulk or epitaxial starting wafer architectures. SOI wafers potentially offer "perfect" transistor isolation (lower leakage), tighter transistor packing density (higher transistor count/higher IC function at the same lithographic resolution), reduced parasitic drain capacitance (faster circuit performance and lower power consumption), and simplified processing relative to bulk or epitaxial silicon wafers. Due to these advantages, SOI wafers appear ideal for leading edge integrated circuits with high speed, high transistor count, low voltage/low power operation, and battery operated systems requirements, such as portable logic or microprocessor ICs. Silicon-on-insulator (SOI) wafers have traditionally been used

for extreme environmental applications, such as high temperature and severe environments (e.g., outer space). However, they are expected to expand into mainstream CMOS applications due to these advantages:

- Excellent lateral [40.60] and vertical isolation of active devices from substrate

- Elimination [55,56] of inter-device leakage and latch-up in CMOS structures

• Effective [111,95] reduction of substrate coupling in RF circuits (allows higher quality inductors with increased Q factor)

• Effective reduction [40,60] of interference and cross-talk between devices in mixed-signal ICs

• Different [96,112] voltages may be used on different devices without the added processing steps required for triple wells

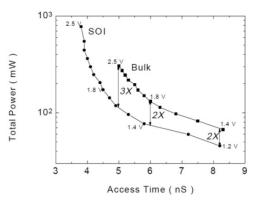

Fig.4.Improvement in execution time by using SOI

• Faster [137,41,61] device operation (speed/power product) due to reduction of parasitic capacitance (primarily due to reduced source-drain junction capacitance, but also from gate-to-substrate capacitance and metal-to-substrate capacitance):

• IBM reported a [72,30] 20% to 35% increase in chip speed for their PowerPC chips.

• Lower power [23,31,12] consumption (speed/power product) due to lower operating voltages on devices and lower parasitic capacitance.

• IBM [13,11,62]reported a 35% to 70% reduction in power consumption for their PowerPC chips.

• More functions[63,32] per die area or reduced die area per function; SOI[110,99] allows tighter layout design rules (higher integration density), mainly due to reduced STI layout area required for lateral junction isolation (resulting from the absence of wells and the possibility of direct contact of the source-drain diodes in the NMOS and PMOS transistors)

• Performance[109,33,24] improvement equivalent to next technology node without scaling (e.g., performance of 0.25 micron devices on SOI wafers equivalent to performance of 0.18 micron devices on bulk wafers)

## IV. COMPARISON BETWEEN SOI CMOS AND BULK CMOS:

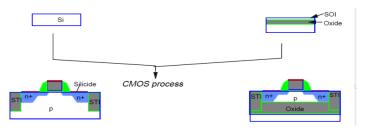

Fig.3. comparison between SOI and bulk CMOS

The difference between bulk CMOS and SOI CMOS are following:

- [23,14,43]Today we are settling everything in small area .When scaling down the device dimensions the doping densities must be increased to maintain proper device behaviour, [74,64,108] which is hard to manage when the device dimensions reach 50 nm and below. However, for thin film devices, such as fully depleted SOI, the doping densities required are lower. This is one reason for why SOI may be more suitable for the future processes in comparison to bulk CMOS.

- The [90,82,83]speed in bulk devices is much determined by the relative magnitude of the parasitic drain and source junction capacitances compared with the gate capacitance, which is increasing as the devices are scaled down and doping levels are increased.

- The [19,38,39]parasitic capacitances of the devices are thereby much smaller in SOI technologies than in bulk technologies. The active volume of silicon is smaller in SOI devices than in bulk technology. The SOI devices are therefore less sensitive to high energy particles and make them suitable for use in radiation hard applications.

- The increases of battery powered equipment strongly increase the demand for integrated circuits operating at a low supply voltage and with minimum power consumption [130,39,28]. This is also a reason for choosing SOI instead of bulk in the future, [20,42] since it is more suited to low voltage applications. In addition, the current drive capability of SOI devices is higher than for bulk devices, which increases the speed of the device. It [73,22]also makes it possible to trade speed/power, to get a device with the same speed performance as the bulk device, but at lower power consumption.

### V. FUTURE SOI APPLICATIONS:

After [83,91]criticizing SOI technology Intel Corp. is now adopting this technology again .Intel is now endorsing SOI with 22nm process technology. Intel will introduce a germanium (III V) channel and full depleted SOI at 22nm. In the recent several quarters Intel has revealing pieces of information about 22nm process technologies that will be used to manufacture Ivry Bridge-generation of microprocessors as well as system-on-chip devices.

The Santa Clara, california based maker of central processing unit displayed its first 22nm test wafer with SRAM memory as well as logic circuits to be used in future Intel microprocessor. Intel has said that in case of 22nm fabrication process Intel's research group had a variety of novel transistors and interconnect ideas in pipepline including III-V channel materials ,multigate transistors, 3-D stacking and others.

### VI. SOI CHALLENGES AND ISSUES:

The [15,34,107]main barrier to the widespread adoption of SOI wafers for mainstream CMOS fabrication in the past has been the uncertain material quality and the higher cost of SOI wafers. However, these wafers are now demonstrating technical (materials quality) and economic (cost) readiness for use in mainstream CMOS IC production.[35,44,64] The key materials quality issues are the continuity and thickness uniformity of the BOX and the defectivity and thickness uniformity of the device-quality, single-crystal silicon layer.

Important BOX defects include voids and inclusions; [106,36,25] the defects in the silicon top layer include threading dislocations and pits (COPs). Also, the interface charge trapped at the interface of the top silicon layer and the BOX must be kept small (less than ~1011/cm2). [The amount of charge at the BOX/silicon layer interface affects the electrical behaviour of SOI CMOS transistors, e.g., threshold voltage and saturation current.] [75,16,26,81] The suppliers of SOI wafers continue to aggressively improve materials quality and reduce cost, driven by the considerable economic motivation of a rapidly growing commercial market for SOI wafers and a clearly defined roadmap for SOI material quality on the ITRS Roadmap [8,105,45,76]. In this fast developing arena, reports of SOI materials quality measurements that are only a year old may be out of date.

Assuming [26,77,80]that the issues of materials quality and cost will be adequately addressed, the adoption of SOI wafers for CMOS fabrication is a non-trivial task. Fabricating CMOS devices in SOI presents challenges in device design and process integration, as well as in the process simulation, device simulation and circuit simulation TCAD tools. For [81,17,65] example, dopant diffusion in the thin silicon layer over the BOX is dramatically altered in SOI by interaction of the diffusing dopants with the silicon/BOX interface (at the top of the BOX) [104,46,66]. This and other differences must be comprehended in process simulations and in process integration for IC fabrication. Adopting SOI wafers is not a simple transfer of a bulk CMOS device fabrication process into an SOI substrate.

There [27,103,102] are also significant differences between the way a bulk or epitaxial silicon CMOS device and an SOI CMOS device behave electrically. For example, "short channel effects" (SCE) are typically suppressed more effectively in SOI CMOS devices than in bulk CMOS, and SOI CMOS devices typically have lower subthreshold leakage ("off current") and higher saturation current ("on current") than bulk CMOS counterparts [5,101,18,37]. Consequently, the SOI CMOS circuits typically demonstrate higher speed performance and lower power dissipation than bulk or epitaxial CMOS. Also, the SOI CMOS device exhibits several parasitic phenomena that are not typically observed in the bulk or epitaxial CMOS device [5,6,132].

These phenomena are related to impact ionization in the high electric field that occurs near the drain in CMOS devices, and the fact that the channel terminal in the SOI CMOS device is isolated from the substrate, unless specific measures, such as body ties [6], are explicitly employed. In other words, the body of the SOI device is "floating". There are several anomalous electrical behaviours in SOI CMOS devices that arise from these "floating body effects" (such as a "kink" in the output I-V characteristic of the SOI CMOS device and degraded drain breakdown voltage). Note that floating body effects are not necessarily all bad, as they may be employed to increase the current output from an SOI CMOS device [6].

The point is that the SOI CMOS transistor is different than the bulk CMOS transistor and these differences must be reflected in the simulators employed to design devices and circuits for CMOS ICs

## International Journal of Engineering Sciences & Emerging Technologies, May 2011.ISSN: 2231 – 6604Volume 1, Issue 1, pp: 1-16 ©IJESET

fabricated in SOI wafers. SOI CMOS transistors also exhibit so-called self-heating effects [5,6,133]. These effects arise in SOI devices because the device is thermally insulated from the substrate by the buried oxide (BOX). Consequently, removal of excess heat generated within the device by device switching is not removed as efficiently in SOI devices as it is in bulk devices. This leads to a substantial elevation of temperature within the SOI device (50-1500C). This modifies the output I-V characteristics of SOI devices, once sufficient power has been dissipated within the devices. Note [93,4,86] that this self-heating effect only appears when power is being dissipated within the device (that is, when the transistor is on, conducting current through its channel). This [87,94]only occurs in CMOS circuits when a logic stage is switching state, not when it is in a stand-by state (e.g., holding a logic high or low state).

Fig.4. Self heating effect in SOI transistor

These effects certainly will not [92,84,29]prevent the widespread adoption of SOI for CMOS ICs, but they must be taken into account by thoughtful device and circuit design approaches that specifically address the peculiarities of the SOI CMOS transistor vs. the bulk or epitaxial wafer CMOS transistor.

Obviously, the process [78,85,93]simulation, device simulation, circuit simulation, and layout TCAD tools employed by designers must accurately model the peculiarities (and advantages) of SOI CMOS to achieve optimal device design, circuit design, layout and processing approaches for CMOS ICs fabricated with SOI wafers. CMOS transistors designed for use with SOI wafers are classified by the thickness of the device-quality single-crystal silicon layer (at the surface above the BOX) relative to the depths of the source-drain junction and channel depletion layers in the device with the operating voltages applied. An SOI CMOS transistor is classified as "partially depleted" (PD) if the silicon surface layer is thicker than the depth of the depletion region in the transistor's channel.

The SOI CMOS transistor is classified as "fully depleted" (FD) if the silicon surface layer is equal to the depth of the depletion region in the transistor's channel. The transistor will be partially depleted or fully depleted depending on the silicon layer thickness above the BOX and the doping concentration in the channel. To form a fully depleted SOI transistor, the channel doping concentration must be low enough the gate depletion region extends throughout the entire thickness of the silicon layer. When the silicon surface layer is thicker than about

200nm, the transistor will typically be partially depleted, unless the channel doping concentration is reduced to such low values that the threshold voltage is too low for practical CMOS applications (less than 100 mV).

If the silicon layer thickness is reduced to about 100nm, the transistor will be fully depleted, even when the channel doping concentration is increased to produce threshold voltages of 300-400mV. If the silicon layer thickness is reduced further (70nm), the transistor will remain fully depleted even if the channel doping concentration is increased to produce even higher threshold voltages (700mV). There are significant differences in partially depleted and fully depleted SOI CMOS transistors [5,134]. For example, the threshold voltage of the fully depleted (FD) device is very sensitive to the silicon surface film thickness. This results in an addition source of manufacturing variance in the fabrication of FD SOI CMOS. Typically, this is on the order of 10mV in threshold voltage per

nanometer of variation in the silicon film over the BOX. This is the main reason why, at the present time, the fabrication of commercial CMOS on SOI typically employs partially depleted (PD) devices. However, careful device design and optimizing the channel implant process can reduce this sensitivity in FD devices.

It [95,88,96] is also important to note that the variation of drain (saturation) current does not have the same sensitivity to film thickness as the threshold voltage in FD SOI CMOS [5,136,135]. There are significant advantages for FD transistors over PD transistors, and the trend in SOI CMOS is toward the use of fully depleted devices. A fundamentally important point is that in FD SOI CMOS the subthreshold slope can be very low (less than ~65 mV/decade (i.e., a 65 mV increase in gate voltage will result in a tenfold increase in the subthreshold drain current). This is [89,10,89]significantly closer to the theoretical minimum (~60 mV/decade) than the typical values of 80-85 mV/decade in PD SOI CMOS and 85-90 mV/decade (best case) in bulk CMOS. This is a critical advantage. It allows the threshold voltage of the FD SOI CMOS device to be very low (150-200mV) with acceptable subthreshold leakage ("off current"), which determines off-state power dissipation. Lowering [98,99]the threshold voltage also means that the supply voltage can be reduced significantly without degrading CMOS IC speed performance (the supply voltage needs to be 4-5 times the threshold voltage; below this ratio, the speed performance of the circuit will degrade rapidly). The [47,67] reduction of the supply voltage produces a significant reduction in active (switching) power dissipation, without unacceptable performance degradation. [Note: [137,79] the active power dissipation is also reduced somewhat by reduction of parasitic capacitance in SOI CMOS relative to bulk CMOS.] Also, in the FD CMOS device the variation of threshold voltage with temperature is significantly less (2-3 times less) than in the PD CMOS device.

Furthermore, [138]in general, the anomalous electrical behaviours arising from floating body effects in SOI CMOS transistors are less of a problem in FD transistors than they are in PD transistors. Consequently, it is expected that FD SOI CMOS transistors will be generally adopted in the near future [1,68,48]. Converting an existing PD SOI CMOS device and circuit design into FD CMOS is expected to be straightforward [7,9], at least in comparison with to the challenges in the conversion from bulk CMOS to SOI CMOS.

### VII. **PERFORMANCE IMPROVEMENTS**:

Here some practical data is showing some comparison between SOI and bulk CMOS. We can see how much the performance is increased when we [49,6] are using the SOI CMOS-

- [141]SOI Ring oscillator frequency up to 20% higher

- [140]Inverter performance up to 10% better

- [139] 2 NAND up to 27% better

- 3 NAND up to 27% better

- 2 NOR up to 27% better

- 3 in NOR up to 25% better

#### **CONCLUSION:**

As the SOI technology becomes more of a mainstream technology it becomes increasingly important to be able to handle and compensate for the unwanted effects introduced when using SOI [148]. Some of the most important effects kink effect, history effect and self heating appears as the most important. Some methods to compensate for these effects were presented. In comparison with bulk the SOI technologies appear to be more suited for the future sub nanometer and low supply voltage technologies. The power consumption is also expected to decrease if SOI [96,97]is used instead of bulk devices.

#### **REFERENCES:**

## International Journal of Engineering Sciences & Emerging Technologies, May 2011.ISSN: 2231 – 6604Volume 1, Issue 1, pp: 1-16 ©IJESET

[1]. G.K. Celler, S. Cristoloveanu, "Frontiers of silicon-on-insulator", Journal Applied Physics, Vol No. 93, (2003), pp. 4955–4978.

[2] E. Simoen, C. Claeys, "The low-frequency noise behaviour of silicon-on-insulator technologies, Solid-State Electron", Vol. No.39, (1996), pp. 949–960.

[3] K. Chang, S. Pamarti, K. Kaviani, E. Alon, X. Shi, T.J. Chin et al. "Clocking and circuit design for a parallel I/O on a first-generation CELL processor", (2005), p. 526.

[4] M. Bruel, "Silicon-on-insulator material technology, Electron Lett", Vol No. 31, (1995), pp. 1201–1202.

[5] G.K. Celler, S. Cristoloveanu, "Frontiers of silicon-on-insulator, Journal Applied Physics", Vol No. 93, (2003), pp. 4955–4978.

[6] C. Claeys, A. Mercha and E. Simoen," Low frequency noise assessment of silicon substrates and process modules for deep submicron CMOS technology nodes", Journal Electrochemical Soc, Vol. No.151, (2004), pp. G307–G318.

[7] J.P. Colinge, "Silicon-on-insulator Technology: Materials to VLSI", (1991).

[8] N.B. Lukyanchikova, "Noise Research in Semiconductor Physics", (1996).

[9] A.L. McWhorter, "1/f noise and germanium surface properties.", (1957), p. 207.

[10] T. Boutchacha, G. Ghibaudo, G. Guégan and M. Haond, " Low frequency noise characterization of 0.25 μm Si CMOS transistors", Journal Non-Crystal Solids, Vol. No. 21, (1997), pp. 192–197.

[11] A. Mercha, E. Simoen and C. Claeys, "Impact of the high vertical field on low frequency noise in deep submicron MOSFETs.", IEEE Trans Electronic Device, Vol. No. 50, (2003), pp. 2520–2527.

[12] F.N. Hooge, "1/f noise is no surface effect", Physics Lett , Vol. No.29 ,(1969), p. 139.

[13] F.N. Hooge, "1/f noise sources", (1994), pp. 1926–1935.

[14] X.S. Li, C. Barros, E.P. Vandamme and L.K.J. Vandamme, "Parameter extraction and 1/f noise in a surface and a bulk-type, p-channel LDD MOSFET, Solid-State Electron" Vol. No. 37, (1994), pp. 1853–1862.

[15] P. Srinivasan, E. Simoen, L. Pantisano, C. Claeys, D. Misra, "Impact of high-k gate stack material with metal gates on LF noise in n- and p-MOSFETs", Microelectronics Eng, Vol. No. 80, (2005), pp. 226–229.

[16] H.-K. Lim , J.G. Fossum, "Threshold voltage of thin-film silicon-on-insulator (SOI) MOSFETs", Vol. No.30, (1983), pp. 1244–1251.

[17] T. Ernst, S. Cristoloveanu, G. Ghibaudo, T. Ouisse, S. Horiguchi and Y. "Ultimately thin double-gate SOI MOSFETs", IEEE Trans Electron Device 50 (2003), pp. 830–838.

[18] S. Haendler, J. Jomaah, F. Dieudonné, F. Balestra, "On the 1/f noise in fully depleted SOI transistors", World Scientific (2001), p. 133.

[19] E. Simoen, A. Mercha, C. Claeys, N. Lukyanchikova and N. Garbar, "Critical discussion of the front-back gate coupling effect on the low-frequency noise in fully depleted SOI MOSFETs", Trans Electronic Device, Vol. No. 51, (2004), pp. 1008–1016.

[20] L. Zafari, F. Daugé, J. Jomaah and G. Ghibaudo, " On the low-frequency noise in fully depleted and double-gate SOI transistors", (2005), p. 147.

[21] N. Sadachika, Y. Uetsuji, D. Kitamaru, H.J. Mattausch, M. Miura-Mattausch, L. Weiss et al., "Fully-depleted SOI-MOSFET model for circuit simulation and its application to 1/f noise analysis." (2004), p. 255.

[22] J. Jomaah, F. Balestra , G. Ghibaudo, "Experimental investigation and numerical simulation of low-frequency noise in thin film SOI MOSFETs", Physics Status Solidi Vol No.142, (1994), pp. 533–537.

[23] S. Haendler, F. Dieudonné, J. Jomaah, F. Balestra, C. Raynaud, J.L. Pelloie, "Impact of front oxide quality on transient effects and low-frequency noise in partially and fully depleted SOI nMOSFETs", Solid-State Electron, Vol. No.46, (2002), pp. 1013–1017.

[24] O. Potavin, S. Haendler, J. Jomaah, F. Balestra , C. Raynaud, "Reliability of ultra-thin film deep submicron SIMOX nMOSFETs", Solid-State Electron, Vol. No.46 ,(2002), pp. 367–371.

[25] Nève A, Dessard V, Delatte P, Brodeoux V, Iñíguez B, Rauly E, et al. "Improvement of sub-0.25 μm fullydepleted SOI CMOS analog performance by thinning the Si film.", 2001–3, p. 271. [26] Zafari L, Jomaah J, Ghibaudo G. "Low frequency noise in multi-gate SOI CMOS devices.", 2006, p. 141.

[27] Eminente S, Cristoloveanu S, Clerc R, Ohata A, Ghibaudo G. "Ultra-thin fully-depleted SOI MOSFETs: special charge properties and coupling effects." ,2006, p. 57.

[28] D. Suh and J.G. Fossum, "A physical charge-based model for nonfully depleted SOI MOSFETs and its use in assessing floating-body effects in SOI CMOS circuits", IEEE Trans Electronic Device, Vol. No. 42, (1995), pp. 728–737.

[29] Y.-C. Tseng, M.W. Huang, D.J. Monk, P. Welch, J.M. Ford, J.C.S. Woo, "AC floating body effects and the resultant analog circuit issues in submicron floating body and body-grounded SOI MOSFET's", IEEE Trans Electronic Device, Vol. No. 46, (1999), pp. 1685–1692.

[30] W. Jin, P.C.H. Chan, S.K.H. Fung, P.K. Ko, "Shot-noise-induced excess low-frequency noise in floatingbody partially depleted SOI MOSFET's", IEEE Trans Electronic Device, Vol. No. 46, (1999), pp. 1180–1185.

[31] J. Chen, P. Fang, P.K. Ko, C. Hu, R. Solomon, T.-Y. Chan et al., "Noise overshoot at drain current kink in SOI MOSFET", (1990), p. 40.

[32] Y.-C. Tseng, W.M. Huang, M. Mendicino, D.J. Monk, P.J. Welch, J.C.S. Woo, "Comprehensive study on low-frequency noise characteristics in surface channel SOI CMOSFETs and device design optimization for RF ICs", IEEE Trans Electronic Device, Vol. No. 48, (2001), pp. 1428–1437.

[33] E. Simoen, U. Magnusson, A.L.P. Rotondaro, C. Claeys, "The kink-related excess low-frequency noise in silicon-on-insulator MOST's", IEEE Trans Electronic Device, Vol. No. 41, (1994), pp. 330–339.

[34] Y.-C. Tseng, W.M. Huang, M. Mendicino, D. Ngo, V. Ilderem, J.C.S. Woo, "Device design methodology to optimize low-frequency noise in advanced SOI CMOS technology for RF IC's", IEDM Technology Dig, (1998), p. 949.

[35] Y.-C. Tseng, W.M. Huang, J.A. Babcock, J.M. Ford , J.C.S. Woo, "Correlation between low-frequency noise overshoot in SOI MOSFETs and frequency dependence of floating body effect", (1997), p. 99.

[36] Y.-C. Tseng, W.-L.M. Huang, P.J. Welch, J.M. Ford, J.C.S. Woo, "Empirical correlation between AC kink and low-frequency noise overshoot in SOI MOSFET's", IEEE Electronic Device Lett, Vol. No. 19, (1998), pp. 157–159.

[37] W. Jin, P.C.H. Chan, S.K.H. Fung , P.K. Ko, "A physically-based low-frequency noise model for NFD SOI MOSFET's", (1998), p. 23.

[38] Y.-C. Tseng, W.M. Huang, C. Hwang, J.C.S. Woo, "AC floating body effects in partially depleted floating body SOI nMOS operated at elevated temperature": IEEE Electronic Device Lett, Vol. No.21, (2000), pp. 494–496.

[39] Y.-C. Tseng, W.M. Huang, M. Mendicino, P. Welch, V. Ilderem , J.C.S. Woo, "Minimizing body instability in deep sub-micron SOI MOSFETs for sub-1V RF applications", VLSI technology dig technical papers, (1999), p. 27.

[40] Y.-C. Tseng, W.M. Huang, C. Hwang, P. Welch, J.C.S. Woo, "Temperature dependence of AC floating body effects in PD SOI nMOS", The IEEE, (1999), p. 26.

[41] Y.-C. Tseng, W.M. Huang, V. Ilderem , J.C.S. Woo, "Floating body induced pre-kink excess low-frequency noise in submicron SOI CMOSFET technology", IEEE Electronic Device Lett, Vol. No. 20, (1999), pp. 484–486.

[42] Dessard V, Flandre D. " Low frequency noise measurements at elevated temperatures on thin-film SOI nMOSFET.", Proceedings of ESSDERC '98; 1998. p. 604.

[43] V. Dessard, B. Iñíguez, S. Adriaensen , D. Flandre, "SOI nMOSFET low-frequency noise measurements and modeling from room temperature up to 250 °C", IEEE Trans Electronic Device, Vol. No. 49, (2002), pp. 1289–1295.

[44] G.O. Workman ,J.G. Fossum, "Physical noise modeling of SOI MOSFET's with analysis of the Lorentzian component in the low-frequency noise spectrum", IEEE Trans Electronic Device, Vol. No. 47, (2000), pp. 1100–1192.

[45] C. Jungemann, B. Neinhüs, C.D. Nguyen, B. Meinerzhagen, "Impact of the floating body effect on noise in SOI devices investigated by hydrodynamic simulation.", simulation of semiconductor processes and devices SISPAD, (2004), p. 235.

[46] F. Faccio, F. Anghinolfi, E.H.M. Heijne, P. Jarron, S. Cristoloveanu, "Noise contribution of the body resistance in partially-depleted SOI MOSFET's", IEEE Trans Electronic Devices Vol. No.45 ,(1998), pp. 1033–1038.

[47] T. Tsuchiya, T. Yoshida , Y. Sato, "Impact of hot-carrier stress on low-frequency noise characteristics in floating-body silicon-on-insulator metal oxide semiconductor field-effect transistors, Jpn", Journal Applied Physics, Vol. No. 41 ,(2002), pp. 4427–4431.

[48] K.-M. Chen, H.-H. Hu, G.-W. Huang, C.-Y. Chang, "Degradation of low-frequency noise in partially depleted silicon-on-insulator metal oxide semiconductor field-effect transistors by hot-carrier stress, Jpn" Journal Applied Physics, Vol. No. 44, (2005), pp. 3832–3835.

[49] N. Lukyanchikova, N. Garbar, A. Smolanka, V. Kudina, C. Claeys, E. Simoen, "Analytical model for the impact of the twin-gate on the floating-body-related low-frequency noise overshoot in silicon-on-insulator MOSFETs", IEEE Trans Electronic Device, Vol. No. 53, (2006), pp. 3118–3128.

[50] Jomaah J, Dixkens D, Pelloie JL, Balestra F. "Impact of latch phenomenon on low frequency noise in SOI MOSFETS.", Proceedings of ESSDERC;, 1996. p. 87.

[51] J. Jomaah , F. Balestra, "Impact of latch phenomenon on low-frequency noise in SOI MOSFETs", Microelectron Reliability, Vol. No. 38, (1998), pp. 567–570.

[52] A. Mercha, J.M. Rafí, E. Simoen, E. Augendre ,C. Claeys, "Linear Kink Effect" induced by valence band electron tunneling in ultra-thin gate oxide bulk and SOI MOSFETs", IEEE Trans Electronic Device, Vol. No. 50, (2003), pp. 1675–1682.

[53] A. Mercha, E. Simoen, H. van Meer, C. Claeys, "Low-frequency noise overshoot in ultra-thin gate oxide silicon-on-insulator metal-oxide-semiconductor field-effect transistors", Applied Physics Lett, Vol. No. 82, (2003), pp. 1790–1792.

[54] F. Dieudonné, J. Jomaah, F. Balestra, "Gate-induced floating body effect excess noise in partially depleted SOI MOSFETs", IEEE Electronic Device Lett, Vol. No. 23, (2002), pp. 737–739.

[55] N.B. Lukyanchikova, M.V. Petrichuk, N. Garbar, A. Mercha, E. Simoen, C. Claeys, "Electron valenceband tunneling-induced Lorentzian noise in deep submicron silicon-on-insulator metal-oxide-semiconductor field-effect transistors", Journal Applied Physics, Vol. No. 94, (2003), pp. 4461–4469.

[56] N. Lukyanchikova, N. Garbar, A. Smolanka, E. Simoen, A. Mercha, C. Claeys, "Short-channel effects in the Lorentzian noise induced by the EVB tunneling in partially-depleted SOI MOSFETs", Solid-State Electron, Vol. No. 48, (2004), pp. 747–758.

[57] E. Simoen, A. Mercha, C. Claeys, N.B. Lukyanchikova, N. Garbar, "Electron Valence Band tunnelling induced excess Lorentzian noise in fully depleted SOI transistors", IEEE, New York (2003), p. 279.

[58] E. Simoen, A. Mercha, J.M. Rafí, C. Claeys, N.B. Lukyanchikova, N. Garbar, "Explaining the parameters of the Electron Valence-Band tunneling related Lorentzian noise in fully depleted SOI MOSFETs", IEEE Electronic Device, Lett, Vol No. 24, (2003), pp. 751–754.

[59] F. Dieudonné, O. Rozeau, J. Jomaah, F. Balestra, "Direct gate tunneling related excess noise in ultra-thin gate oxide partially depleted SOI MOSFETs", ultimate integration of silicon,(2003), p.

[60] N. Lukyanchikova, N. Garbar, A. Smolanka, E. Simoen, C. Claeys, "Excess Lorentzian noise in partiallydepleted SOI nMOSFETs induced by an accumulation back-gate bias", IEEE Electronic Device Lett, Vol. No. 25, (2004), pp. 433–436.

[61] E. Simoen, A. Mercha, J.M. Rafí, C. Claeys, N.B. Lukyanchikova , A.M. Smolanka et al., "High-energy proton irradiation induced changes in the linear-kink noise overshoot of 0.10 μm partially depleted silicon-on-insulator metal-oxide-semiconductor field-effect transistors," ,Journal Applied Physics,Vol. No. 95, (2004), pp. 4084–4092.

[62] Lukyanchikova N, Garbar N, Smolanka A, Simoen E, Claeys C. "Impact of the back-gate bias on the low-frequency noise of partially depleted silicon-on-insulator MOSFETs." Proceedings of noise in devices and circuits II, Proceedings of SPIE, 5470; 2004. p. 208.

[63] N. Lukyanchikova, N. Garbar, A. Smolanka, E. Simoen, C. Claeys, "Back-gate induced noise overshoot in partially-depleted SOI MOSFETs.", Science and technology of semiconductor-on-insulator structures and devices operating in a harsh environment, (2005), p. 255.

[64] N. Lukyanchikova, N. Garbar, A. Smolanka, M. Lokshin, E. Simoen , C. Claeys, "Origin of the frontback-gate coupling in partially depleted and fully depleted silicon-on-insulator metal-oxide-semiconductor fieldeffect transistors with accumulated back gate", Journal Applied Physics, Vol. No. 98, (2005), p. 114506.

[65] M.J. Kirton, M.J. Uren, "Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise", Advance Physics, Vol. No. 38, (1989), pp. 367–468.

[66] H.M. Bu, Y. Shi, X.L. Yuan, Y.D. Zheng, S.H. Gu, H. Majima et al., "Impact of the device scaling on the low-frequency noise in nMOSFETs", Applied Physics, Vol. No. 71, (2000), pp. 133–136.

[67] Y. Shi, H.M. Bu, X.L. Yuan, S.L. Gu, B. Shen , P. Han et al., "Switching kinetics of interface states in deep submicrometre SOI nMOSFETs", Semiconductor Science Technology, Vol. No. 16, (2001), pp. 21–25.

[68] M.J. Deen, O. Marinov, "Noise in advanced electronic devices and circuits". ICNF 2005, American Institute of Physics (2005), p. 3.

[69] N. Lukyanchikova, M. Petrichuk, N. Garbar, E. Simoen, C. Claeys, "Back front interface related generation-recombination noise in buried-channel SOI pMOSFET's", IEEE Trans Electronic Device, Vol. No.43, (1996), pp. 417–423.

[70] N.B. Lukyanchikova, M.V. Petrichuk, N.P. Garbar, E. Simoen and C. Claeys, "Non-trivial GR and 1/f noise generated in the p-Si layer of SOI and SOS MOSFETs near the inverted front or buried p-Si/SiO2 interface", Semiconductor Science Technology, Vol. No. 14, (1999), pp. 775–783.

[71] N.B. Lukyanchikova, M.V. Petrichuk, N.P. Garbar, E. Simoen, C. Claeys, "Physical model of GR noise observed under inversion conditions near the pSi/SiO2 interfaces in SIMOX submicron MOSFETs and its implications on defect characterisation." international semiconductor device research symposium – ISDRS, (1997), p. 131.

[72] D.S. Ang, Z. Lun, C.H. Ling, "Generation-recombination noise in the near fully depleted SIMOX nMOSFET operating in the linear regime", IEEE Electronic Device Lett, Vol. No. 22, (2001), pp. 545–547.

[73] D.S. Ang, Z. Lun, C.H. Ling, "Generation-recombination noise in the near fully depleted SIMOX SOI nMOSFET – Physical characteristics and modelling", IEEE Trans Electronic Device, Vol. No. 50, (2003), pp. 2490–2498.

[74] H.D. Xiong, B. Jun, D.M. Fleetwood, R.D. Schrimpf, J.R. Schwank, "Charge trapping and low frequency noise in SOI buried oxides", IEEE Trans Nuclear Science, Vol. No. 51, (2004), pp. 3238–3242.

[75] J.R. Schwank, D.M. Fleetwood, H.D. Xiong, M.R. Shaneyfelt, B.L. Draper, "Generation of metastable electron traps in the near interfacial region of SOI buried oxides by ion implantation and their effect on device properties", Microelectronic Eng, Vol. No. 72, (2004), pp. 362–366.

[76] S. Haendler, J. Jomaah, F. Balestra, J.L. Pelloie ,C. Raynaud, "Kink-related excess noise in deep submicron partially and moderately fully depleted Unibond n-metal oxide semiconductor field effect transistor (MOSFET), Jpn", Journal Applied Physics, Vol. No. 39, (2000), pp. 2261–2263.

[77] S.-H. Renn, J. Jomaah, C. Raynaud, F. Balestra, "Investigation of the reliability of Unibond and SIMOX nMOSFETs using charge pumping and noise techniques", Electronic Lett, Vol. No. 34, (1998), pp. 1788–1789.

[78] T. Ushiki, H. Ishino, T. Ohmi, "Effect of starting SOI material quality on low-frequency noise characteristics in partially depleted floating-body SOI MOSFETs", IEEE Electronic Device Lett, Vol. No. 21, (2000), pp. 610–612.

[79] Lartigau I, Routoure J-M, Carin R, Mercha A, Simoen E, Claeys C. "Low temperature noise spectroscopy of 0.1  $\mu$ m partially depleted silicon on insulator MOSFETs." conference on noise and fluctuations – ICNF, 2003. p. 763.

[80] M.N. Ericson, C.L. Britton Jr., J.M. Rochelle, B.J. Blalock, D.M. Binkley, A.L. Wintenberg., "Flicker noise behaviour of MOSFETs fabricated in 0.5 μm fully depleted (FD) silicon-on-sapphire (SOS) CMOS in weak, moderate, and strong inversion", IEEE Trans Nuclear Science, Vol. No. 50, (2003), pp. 963–968.

[81] S. Maeda, Y. Wada, K. Yamamoto, H. Komurasaki, T. Matsumoto, Y. Hirano, "Feasibility of 0.18 μm SOI CMOS technology using hybrid trench isolation with high resistivity substrate for embedded RF/analog applications", IEEE Trans Electronic Device, Vol. No. 48, (2001), pp. 2065–2073.

[82] N.B. Lukyanchikova, M.V. Petrichuk, N.P. Garbar, L.S. Riley ,S. Hall, "A study of noise in surface and buried channel SiGe MOSFETs with gate oxide grown by low temperature plasma anodization", Solid-State Electronic device, Vol No. 46, (2002), pp. 2053–2061.

[83] L.S. Riley ,S. Hall, "X-ray photoelectron spectroscopy of SiGe: implications for oxidation kinetics of SiGe", Journal Applied Physics, Vol. No. 85, (1999), pp. 1–10.

[84] A. Asai, J.S. Iwanaga, A. Inoue, Y. Hara, Y. Kanzawa, H. Sorada, "Low-frequency noise characteristics in SiGe channel heterostructure dynamic threshold pMOSFET (HDTMOS)", IEDM Technology Dig, (2002), p. 35.

[85] A. Inoue, A. Asai, Y. Kawashima, H. Sorada, Y. Kanzawa, T. Kawashima., "Low frequency noise (LFN) characteristics of SiGe channel SOI dynamic threshold MOSFETs (SiGe-SOI-DTMOS) for low-power applications", Proceedings IEEE international SOI conference, (2003), p. 149.

[86] T.-L. Hsu, D.D.-L. Tang , J. Gong, Low-frequency noise properties of dynamic-threshold (DT) MOSFET's, IEEE Electron Device Lett, Vol. No. 20, (1999), pp. 532–534.

[87] M. von Haartman, J. Hållstedt, J. Seger, B.G. Malm, P.-E. Hellström, M. Östling, "Low-frequency noise in SiGe channel pMOSFETs on ultra-thin body SOI with Ni-silicided source/drain.", Proceedings 18th international conference on noise and fluctuations – ICNF, (2005), p. 307.

[88] P. Srinivasan, E. Simoen, D. Misra, C. Claeys, "1/f noise performance of MOSFETs with HfO2 and metal gate on Ge-on-Insulator substrates, Mat Sci Semicond Proc" Vol. No.9, (2006), pp. 721–726.

[89] J.A. Babcock, D.K. Schroder, Y.-C. Tseng, "Low-frequency noise in near-fully-depleted TFSOI MOSFET's", IEEE Electronic Device Lett, Vol. No. 19, (1998), pp. 40–43.

[90] J.A. Babcock, P. Francis, H. Haggag, J. Darmawan, T.-W. Lee, P. Lindorfer., "Effect of body-to-source bias on the analog characteristics of 0.35 μm partially depleted SOI CMOS for low-voltage low-power mixed-mode applications", IEEE international SOI conference, (1998), p. 25.

[91] F. Dieudonné, S. Haendler, J. Jomaah , F. Balestra, "A comparative approach of low frequency noise in 0.25 and 0.12  $\mu$ m partially and fully depleted SOI nMOSFETs", IEEE international SOI Conference, (2002), p. 105.

[92] F. Dieudonné, S. Haendler, J. Jomaah , F. Balestra, "Shrinking from 0.25 down to 0.12 μm SOI CMOS technology node: a contribution to low-frequency noise in partially depleted nMOSFETs", Solid-State Electronic device ,Vol. No.47, (2003), pp. 1213–1218.

[93] F. Dieudonné, S. Haendler, J. Jomaah , F. Balestra, "Low frequency noise in 0.12 μm partially and fully depleted SOI technology", Microelectronic Reliab, Vol. No. 43, (2003), pp. 243–248.

[94] F. Dieudonné, S. Haendler, J. Jomaah , F. Balestra, "Low frequency noise and hot-carrier reliability in advanced SOI MOSFETs", Solid-State Electron, Vol. No. 48, (2004), pp. 985–997.

[95] P. Morfouli, G. Ghibaudo, T. Ouisse, E. Vogel, W. Hill, V. Misra., "Low-frequency noise characterization of n- and p-MOSFETs with ultrathin oxynitride gate films", IEEE Electronic Device Lett, Vol. No.17, (1996), pp. 395–397.

[96] M. Da Rold, E. Simoen, S. Mertens, M. Schaekers, G. Badenes S. Decoutere, "Impact of nitridation of SiO2 gate oxide on 1/f noise in 0.18 μm CMOS", Microelectronic Reliab, Vol. No. 41/42, (2001), pp. 1933–1940.

[97] Lukyanchikova N, Petrichuk M, Garbar N, Simoen E, Mercha A, van Meer H, . "On the origin of the 1/f1.7 noise in deep submicron partially depleted SOI transistors.", Proceedings of ESSDERC, 2002. p. 75.

[98] N. Lukyanchikova, M. Petrichuk, N. Garbar, E. Simoen, A. Mercha, C. Claeys ., "The 1/f1.7 noise in submicron SOI MOSFETs with 2.5 nm nitrided gate oxide", IEEE Trans Electronic Device, Vol. No. 49, (2002), pp. 2360–2367.

[99] A. Vandooren, A.V.Y. Thean, Y. Du, I. To, J. Hughes and T. Stephens, "Mixed-signal performance of sub-100 nm fully-depleted SOI devices with metal gate, high K (HfO2) dielectric and elevated source/drain extensions", IEDM Tech Dig, (2003), p. 975.

[100] A.V.-Y. Thean, A. Vandooren, S. Kalpat, Y. Du, I. To, J. Hughes , "Performance and reliability of sub-100 nm TaSiN metal gate fully-depleted SOI devices with high-k (HfO2) gate dielectric", Symposium on VLSI Technical Dig Tech Papers, (2004), p. 106. [101] C. Claeys, E. Simoen, A. Mercha, L. Pantisano, E. Young, "Low-frequency noise study of nMOSFETs with HfO2 gate dielectric", Journal Electrochemical Soc, Vol. No. 152, (2005), pp. F115–F123.

[102] J.-S. Lee, D. Ha, Y.-K. Choi, T.-J. King ,J. Bokor, "Low-frequency noise characteristics of ultrathin body p-MOSFETs with molybdenum gate", IEEE Electronic Device Lett, Vol. No. 24, (2003), pp. 31–33.

[103] H.S. Momose, H. Kimijima, S.-I. Ishizuka, Y. Miyahara, T. Ohguro , T. Yoshitomi , "A study of flicker noise in n- and p-MOSFETs with ultra-thin gate oxide in the direct-tunneling regime", IEDM Tech Dig, (1998), p. 923.

[104] H. Lee, J.-H. Lee, H. Shin, Y.J. Park , H.S. Min, "Low-frequency noise degradation caused by STI interface effects in SOI-MOSFETs", IEEE Electronic Device Lett, Vol. No. 22, (2001), pp. 449–451.

[105] H. Lee, J.-H. Lee, H. Shin, Y.-J. Park, H.S. Min, "An anomalous device degradation of SOI narrow width devices caused by STI edge influence", IEEE Trans Electronic Device, Vol. No.49, (2002), pp. 605–612.

[106] H.V. Deshpande, B. Cheng , J.C.S. Woo, "Sub-micron fully depleted lateral asymmetric channel SOI MOSFETs for analog and mixed mode applications", Proceedings of the 2000 IEEE international SOI conference, (2000), p. 54.

[107] M.A. Pavanello, J.A. Martino , D. Flandre, "Graded-channel fully depleted silicon-on-insulator nMOSFET for reducing the parasitic bipolar effects", Solid-State Electron, Vol. No. 44, (2000), p. 917.

[108] M.A. Pavanello, J.A. Martino, D. Flandre, "Analog performance and application of graded-channel fully depleted SOI MOSFETs", Solid-State Electron ,Vol. No.44, (2000), p. 1219.

[109] A. Kranti, T.M. Chung, D. Flandre , J.-P. Raskin, "Laterally asymmetric channel engineering in fully depleted double gate SOI MOSFETs for high performance analog applications", Solid-State Electron, Vol. No. 48, (2004), p. 947.

[110] A. Cerdeira, M.A. Alemán, M.A. Pavanello, J.A. Martino, L. Vancaillie, D. Flandre, "Advantages of the graded-channel SOI FD MOSFET for application as a quasi-linear resistor", IEEE Trans Electronic Device, Vol. No. 52, (2005), p. 967.

[111] Simoen E, Claeys C, Chung TM, Flandre D, Raskin J-P. "The low-frequency noise behavior of graded-channel SOI nMOSFETs." EUROSOI Workshop, Grenoble, France, 2006. p. 105.

[112] Simoen E, Claeys C, Chung TM, Pavanello MA, Martino JA, Flandre D. "The low-frequency noise behaviour of graded-channel SOI nMOSFETs. Solid-State Electron, in press," 2007.

[113] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance", IEEE Electronic Device Lett, Vol. No.8, (1987), pp. 410–412.

[114] D. Hasimoto, T. Kaga, Y. Kawamoto, E. Takeda, "A fully depleted lean-channel transistor (DELTA) – A novel vertical ultra thin SOI MOSFET", IEDM Tech Dig, (1989), p. 833.

[115] S. Venkatesan, G.W. Neudeck, R.F. Pierret, "Dual-gate operation and volume inversion in n-channel SOI MOSFET's", IEEE Electronic Device Lett, Vol. No.1, (1992), pp. 44–46.

[116] J.P. Colinge, M.H. Gao, A. Romano-Rodriguez, H. Maes, C. Claeys, "Silicon-on-insulator 'gate-all-around device", IEDM Tech Dig, The IEEE, (1990), p. 595.

[117] E. Simoen, U. Magnusson ,C. Claeys, "A low-frequency noise study of gate-all-around SOI transistors", IEEE Trans Electronic Device, Vol. No. 40, (1993), pp. 2054–2059.

[118] E. Simoen, C. Claeys, S. Coenen and M. Decreton, D.C. and low frequency noise characteristics of  $\gamma$ -irradiated gate-all-around silicon-on-insulator MOS transistors, Solid-State Electron, Vol. No. 38, (1995), pp. 1–8.

[119] J. Kedzierski, D.M. Fried, E.J. Nowak, T. Kanarsky, J.H. Rankin, H. Hanafi et al., "High-performance symmetric-gate and CMOS-compatible Vt asymmetric FinFET devices", IEDM Tech Dig, The IEEE, New York (2001), p. 437.

[120] Y.-K. Choi, T.-J. King and C. Hu, Nanoscale CMOS spacer FinFET for the terabit era, IEEE Electron Dev Lett, Vol. No. 23, (2002), pp. 25–27.

[121] J.-S. Lee, Y.-K. Choi, D. Ha, T.-J. King , J. Bokor, "Low-frequency noise characteristics in p-channel FinFETs", IEEE Electronic Device Lett, Vol. No. 23,(2002), pp. 722–724.

[122] J.-S. Lee, Y.-K. Choi, D. Ha, S. Balasubramanian, T.-J. King, J. Bokor, "Hydrogen annealing effect on DC and low-frequency noise characteristics in CMOS FinFETs", IEEE Electronic Device Lett, Vol. No. 24, (2003), pp. 186–188.

[123] V. Subramanian, A. Mercha, A. Dixit, K.G. Anil, M. Jurczak, K. De Meyer, "Geometry dependence of 1/f noise in n- and p-channel MuGFETs.", 18th international conference on noise and fluctuations – ICNF, (2005), p. 279.

[124] V. Subramanian, B. Parvais, J. Borremans, A. Mercha, D. Linten , P. Wambacq "Device and circuit-level analog performance trade-offs: a comparative study of planar bulk FETs versus FinFETs", IEDM Tech Dig, (2005), p. 898.

[125] Subramanian V, Mercha A, Parvais B, Loo J, Gustin C, Dehan M. Optimization of FinFET geometries for analog performance. ULIS 2006 –seventh international conference on ultimate integration of silicon, Grenoble; 2006. p. 21.

[126] F. Crupi, B. Kaczer, R. Degraeve, V. Subramanian, P. Srinivasan and E. Simoen et al., Reliability comparison of triple-gate versus planar SOI FETs, IEEE Trans Electron Dev 53 (2006), pp. 2351–2357.

[127] Akarvardar K, Cristoloveanu S, Dufrene B, Gentil P, Schrimpf RD, Blalock BJ, et al. Evidence for reduction of noise and radiation effects in G4-FET depletion-all-around operation., ESSDERC; 2005. p. 89.

[128] K. Akarvardar, B.M. Dufrene, S. Cristoloveanu, P. Gentil, B.J. Blalock and M.M. Mojarradi, Low-frequency noise in SOI four-gate transistors, IEEE Electronic Device, Vol. No. 53, (2006), pp. 829–835.

[129] J.A. Babcock, W.M. Huang, J.M. Ford, D. Ngo, D.J. Spooner and S. Cheng, Low-frequency noise dependence of TFSOI BiCMOS for low power RF mixed-mode applications, IEDM Tech Dig, The IEEE, New York (1996), p. 133.

[130] Babcock JA, Loftin B, Madhani P, Chen X, Pinto A, Schroder DK. Comparative low frequency noise analysis of bipolar and MOS transistors using an advanced complementary BiCMOS technology. IEEE 2001 custom integrated circuits conference; 2001. p. 385.

[131] I.Z. Mitrovic, O. Buiu, S. Hall, D.M. Bagnall, P. Ashburn, "Review of SiGe HBTs on SOI", Solid-State Electron, Vol. No. 49,, (2005), pp. 1556–1567.

[132] N. Lukyanchikova, N. Garbar, A. Smolanka, M. Lokshin, S. Hall , O. Buiu et al., "1/f noise and generation/recombination noise in SiGe HBTs on SOI, IEEE Trans Electronic Device, Vol. No. 52, (2005), pp. 1468–1477.

[133] N. Lukyanchikova, N. Garbar, A. Smolanka, M. Lokshin, S. Hall, O. Buiu et al., "Low-frequency noise in SOI SiGe HBTs made by selective growth of the Si collector and non-selective growth of SiGe base". 18th international conference on noise and fluctuations – ICNF (2005), p. 265.

[134] N. Lukyanchikova, N. Garbar, A. Smolanka, M. Lokshin, S. Hall ,O. Buiu ., "The base current and related 1/f noise for SiGe HBTs realized by SEG/NSEG technology on SOI and bulk substrates", Mat Sci Semiconductor Proc, Vol. No. 9, (2006), pp. 727–731.

[135] Y.-C. Tseng, W.M. Huang, M. Mendicino, D. Ngo, V. Ilderem , J.C.S. Woo, "Device design methodology to optimize low-frequency noise in advanced SOI CMOS technology for RF IC's", IEDM Tech Dig, (1998), p. 949.

[136] Y.-C. Tseng, W.M. Huang, E. Spears, D. Spooner, D. Ngo ,J.M. Ford , "Phase noise characteristics associated with low-frequency noise in submicron SOI MOSFET feedback oscillator for RF IC's", IEEE Electronic Device Lett, Vol. No.20, (1999), pp. 54–56.

[137] M. Chan, B. Yu, Z.-J. Ma, C.T. Nguyen, C. Hu, P.K. Ko, "Comparative study of fully depleted and bodygrounded non-fully depleted SOI MOSFET's for high performance analog and mixed signal circuits", IEEE Trans Electronic Device, Vol. No. 42, (1995), pp. 1975–1981.

[138] H. Lee, J.-H. Lee, Y.J. Park , H.S. Min, "Time-varying body instability and low-frequency noise characteristics of mini-field-dual-body silicon-on-insulator structure for analog-digital mixed-mode circuits, Jpn", Journal Applied Physics, Vol. No. 41, (2002), pp. 1279–1283.

[139] Zafari L, Jomaah J, Ghibaudo G. "Floating body effects in 90 nm partially depleted MOSFETs." seventh international conference on ultimate integration of silicon, 2006. p. 157.

[140] S. Haendler, J. Jomaah, F. Balestra and J.L. Pelloie, "Comparative low frequency noise analysis in various SOI devices: Floating body, body-tied, DTMOS with and without current limiter", 2000 IEEE international SOI conference .p. 126.

[141] Haendler S, Jomaah J, Balestra F, Pelloie JL. "On the noise in dynamic threshold (DT) MOS/SOI transistors." ESSDERC; 2000. p. 504–7.

[142] S. Haendler, J. Jomaah, G. Ghibaudo , F. Balestra, "Improved analysis of low frequency noise in dynamic threshold MOS/SOI transistors", Microelectronics Reliab, Vol. No. 41, (2001), pp. 855–860.

[143] M.-H. Gao, J.-P. Colinge, L. Lauwers, S. Wu ,C. Claeys, "Twin-MOSFET structure for suppression of kink and parasitic bipolar effects in SOI MOSFET's at room and liquid helium temperatures", Solid-State Electron, Vol. No. 35, (1992), pp. 505–512.

[144] E. Simoen, P.I.L. Smeys ,C. Claeys, "The low-frequency noise overshoot in partially depleted n-channel silicon-on-insulator twin-MOSTs", IEEE Trans Electronic Device, Vol. No. 41, (1994), pp. 1972–1977.

[145] Simoen E, Claeys C, Lukyanchikova N, Garbar N,A. Smolanka "Electron valence-band tunnelling excess noise in twin-gate silicon-on-insulator MOSFETs." ULIS 2006 – sixth international conference on ultimate integration of silicon; 2006. p. 113.

[146] E. Simoen, C. Claeys, N. Lukyanchikova, N. Garbar and A. Smolanka, "Linear-kink-noise suppression in partially depleted SOI using the twin-gate MOSFET configuration", IEEE Electronic Device Lett, Vol. No. 26, (2005), pp. 510–512.

[147] E. Simoen, C. Claeys, N. Lukyanchikova, N. Garbar, A. Smolanka, P. Ghedini Der Agopian, "Electron valence-band tunneling excess noise in twin-gate silicon-on-insulator MOSFETs", Solid-State Electron, Vol. No. 50, (2006), pp. 52–57.

[148] P. Ghedini Der Agopian, J.A. Martino, E. Simoen, C. Claeys, "Impact of the twin-gate structure on the linear kink effect in PD SOI nMOSFETs", Microelectronics, Journal, Vol. No. 37, (2006), pp. 681–685.